Students in EECS 413 awarded prizes for their circuit designs

The specifications for the projects were close to the state of the art. Congratulations to the winning groups!

The course Monolithic Amplifier Circuits (EECS 413) has a tradition of offering prizes for the top final projects designed by the students, thanks to the support of industry. This year Cirrus Logic, Inc. sponsored the contest.

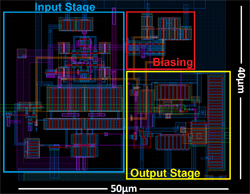

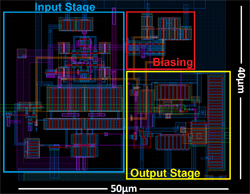

The 58 students in EECS 413 formed 15 project groups. Each group developed their own project ideas. The specifications for the projects were close to the state of the art. Designs were implemented in a commercial 0.13μm CMOS process.

The winning projects for the Fall 2012 course were:

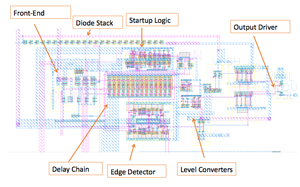

A Rail to Rail Class AB Amplifier (1st place and $1,500)

Haitao Wang, Adam Mendrela, Wenjia Wang, and Brandon Maierle

Enlarge

Enlarge

Enlarge

Enlarge

According to the team, Rail-To-Rail (RTR) operation of an amplifier is desired in order to fully utilize the maximum signal swing. Rail-to-rail operation becomes more and more important in modern CMOS technologies with low supply voltage. The team designed, simulated and laid out a robust, constant-gain rail-to-rail Class AB amplifier, which meets the state-of-the-art specifications. They included a novel adaptive feedback biasing technique to address the intrinsic problems in RTR design, as well as a novel bias replica circuit to provide robust operation under varying conditions.

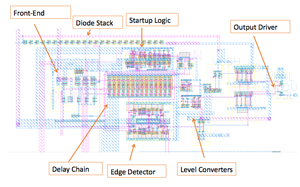

Ultra Low Power Crystal Oscillator (2nd place and $500)

Yi Yuan, Shiming Song, and Zachary Lyzen

Enlarge

Enlarge

Enlarge

Enlarge

There has been significant interest in large scale, wireless sensor networks in recent years. A key limitation of these sensor networks is the power supply. To extend the lifetime of such systems, the team designed an ultra-low power 10 nW crystal oscillator using DLL-assisted pulse injection. Power consumption is minimized by using a pulse injection scheme to drive a 32.768 kHz crystal at 100 mV amplitude. A near threshold voltage domain is used for further power reduction. Pulse timing and width are stabilized through the use of a delay locked loop, which is power gated to run at a 10 percent (the 10 nW number doesn’t use power gating but assumes steady state conditions on the biasing caps) duty cycle. This work was based on the paper, A 5.58nW 32.768kHz DLL-Assisted XO for Real-Time Clocks in Wireless Sensing Applications,” by Dongmin Yoon, Dennis Sylvester, David Blaauw. Proc. ISSCC 2012.

The entire class served as judges this year. Watch a video about EECS 413.

MENU

MENU