Student teams earn prizes for their analog/digital interface circuit designs in EECS 511

The students, lead by Prof. Michael Flynn, competed for cash prizes—the two winners were chosen by Analog Devices.

Enlarge

Enlarge

Enlarge

Enlarge

Students in the graduate level course, Integrated Analog/Digital Interface Circuits (EECS 511), competed for cash prizes while presenting their final design projects thanks to the support of Analog Devices, Inc. EECS 511 is taught by Prof. Michael Flynn, an expert in analog and mixed-signal circuits, analog-to-digital conversion, and other interface circuits.

The top three projects were sent to Analog Devices, where a group of six senior circuit designers selected two winners. First place and $1,500 went to Chia-Hsiang Chen, Kunjay Shah, Madin Kim, and Zhao Xu for their project, “Log SAR ADC.” Second place and $500 went to Jihyun Cho, Wai Wah Chan, Jing Hu, and Phil Knag for their project, “A 10-bit 1MS/s 23.8 fJ/conversion-step Asynchronous SAR ADC with Error Compensation.”

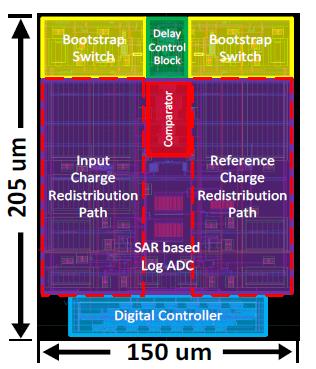

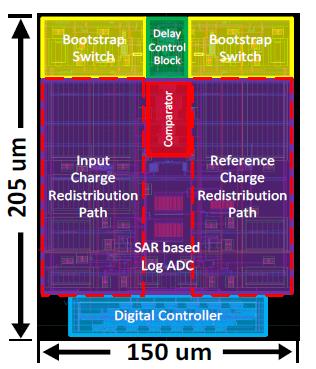

First Place: Log SAR ADC

Enlarge

Enlarge

Enlarge

Enlarge

The students described their project as follows:

Natural signals, such as earthquake waveforms or neural signals, usually have a very wide dynamic range which makes linear digitization less effective because of the requirement of a large number of quantization bits. Previous work has shown that recording such signals in the logarithmic scale is more efficient. Successful log ADC examples include a pipeline structure and a log diode structure. In this work, we implement a log ADC based on the successive approximate register (SAR) ADC topology. Unlike base-10 logarithm or base-e logarithm ADCs from previous work, our log ADC digitizes signals to a base of 2 which enhances digital computation.

This paper presents a novel resolution-reconfigurable algorithm and a prototype of SAR-based Log ADC. This Log ADC can achieve 34.2dB SNDR at 25MS/s. We also show that, by utilizing charging sharing effects, only one reference voltage is required. The system is implemented in 130nm CMOS process and has a core area as 0.0308mm2.

Second Place: A 10-bit 1MS/s 23.8 fJ/conversion-step Asynchronous SAR ADC with Error Compensation

Enlarge

Enlarge

The students described their project as follows:

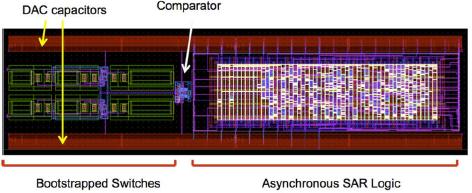

Successive approximation register (SAR) analog-to-digital converters are a popular choice and are extensively employed in low-power and low-speed applications. This work presents a 10-bit 1MS/s 23.8 fJ/conversion-step asynchronous SAR ADC for applications in areas such as wireless sensor networks and bio-medical sensors. This work builds upon and consolidates the SAR error correction scheme proposed [by others] and includes a monotonic switching scheme to enable a low power SAR converter with high SNDR. The architecture is implemented in 0.13μm CMOS.

Enlarge

Enlarge

MENU

MENU